# NEHRU COLLEGE OF ENGINEERING AND RESEARCH CENTRE (NAAC Accredited)

(Approved by AICTE, Affiliated to APJ Abdul Kalam Technological University, Kerala)

## DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

## **COURSE MATERIALS**

## EC 308:EMBEDDED SYSTEMS

#### VISION OF THE INSTITUTION

To mould true citizens who are millennium leaders and catalysts of change through excellence in education.

#### MISSION OF THE INSTITUTION

**NCERC** is committed to transform itself into a center of excellence in Learning and Research in Engineering and Frontier Technology and to impart quality education to mould technically competent citizens with moral integrity, social commitment and ethical values.

We intend to facilitate our students to assimilate the latest technological know-how and to imbibe discipline, culture and spiritually, and to mould them in to technological giants, dedicated research scientists and intellectual leaders of the country who can spread the beams of light and happiness among the poor and the underprivileged.

#### ABOUT DEPARTMENT

• Established in: 2002

♦ Course offered: B.Tech in Electronics and Communication Engineering

M.Tech in VLSI

♦ Approved by AICTE New Delhi and Accredited by NAAC

◆ Affiliated to the University of Dr. A P J Abdul Kalam Technological University.

## **DEPARTMENT VISION**

Providing Universal Communicative Electronics Engineers with corporate and social relevance towards sustainable developments through quality education.

#### **DEPARTMENT MISSION**

- 1) Imparting Quality education by providing excellent teaching, learning environment.

- 2) Transforming and adopting students in this knowledgeable era, where the electronic gadgets (things) are getting obsolete in short span.

- 3) To initiate multi-disciplinary activities to students at earliest and apply in their respective fields of interest later.

- 4) Promoting leading edge Research & Development through collaboration with academia & industry.

#### PROGRAMME EDUCATIONAL OBJECTIVES

PEOI. To prepare students to excel in postgraduate programmes or to succeed in industry / technical profession through global, rigorous education and prepare the students to practice and innovate recent fields in the specified program/ industry environment.

PEO2. To provide students with a solid foundation in mathematical, Scientific and engineering fundamentals required to solve engineering problems and to have strong practical knowledge required to design and test the system.

PEO3. To train students with good scientific and engineering breadth so as to comprehend, analyze, design, and create novel products and solutions for the real life problems.

PEO4. To provide student with an academic environment aware of excellence, effective communication skills, leadership, multidisciplinary approach, written ethical codes and the life-long learning needed for a successful professional career.

## **PROGRAM OUTCOMES (POS)**

## **Engineering Graduates will be able to:**

- 1. **Engineering knowledge**: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

- 2. **Problem analysis**: Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

- 3. **Design/development of solutions**: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

- 4. **Conduct investigations of complex problems**: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

- 5. **Modern tool usage**: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

- 6. **The engineer and society**: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- 7. **Environment and sustainability**: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- 8. **Ethics**: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- 9. **Individual and team work**: Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

- 10. **Communication**: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

- 11. **Project management and finance**: Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

- 12. **Life-long learning**: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

## PROGRAM SPECIFIC OUTCOMES (PSO)

**PSO1**: Ability to Formulate and Simulate Innovative Ideas to provide software solutions for Real-time Problems and to investigate for its future scope.

**PSO2**: Ability to learn and apply various methodologies for facilitating development of high quality System Software Tools and Efficient Web Design Models with a focus on performance

optimization.

**PSO3**: Ability to inculcate the Knowledge for developing Codes and integrating hardware/software products in the domains of Big Data Analytics, Web Applications and Mobile Apps to create innovative career path and for the socially relevant issues.

# COURSE OUTCOMES EC 308

| SUBJECT CODE: EC 308 |                                                                          |  |  |  |  |  |  |

|----------------------|--------------------------------------------------------------------------|--|--|--|--|--|--|

|                      | COURSE OUTCOMES                                                          |  |  |  |  |  |  |

| C308.1               | Ability to understand basics of embedded system and to design an         |  |  |  |  |  |  |

|                      | embedded system product.                                                 |  |  |  |  |  |  |

| C308.2               | Ability to understand the different standards and protocols used for     |  |  |  |  |  |  |

|                      | communication with I/O devices.                                          |  |  |  |  |  |  |

| C308.3               | Ability to distinguish different ways of communication with I/O devices. |  |  |  |  |  |  |

| C308.4               | Ability to understand basic programming concepts of Embedded Systems     |  |  |  |  |  |  |

| C308.5               | Ability to understand about inter-process communication.                 |  |  |  |  |  |  |

| C308.6               | Ability to design real time embedded systems using the concepts of RTOS. |  |  |  |  |  |  |

## MAPPING OF COURSE OUTCOMES WITH PROGRAM OUTCOMES

| CO'S   | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|

| C308.1 |     |     | 3   |     |     |     |     |     |     |      |      | 1    |

| C308.2 | 2   | 3   | 3   |     | 2   |     |     | 2   |     |      |      | 1    |

| C308.3 | 2   | 3   | 3   | 3   | 2   | 3   | 2   |     |     |      | 2    | 1    |

| C308.4 |     | 3   | 3   | 3   |     | 3   |     |     |     |      |      | 1    |

| C308.5 |     |     | 3   |     | 2   |     |     |     |     |      |      | 1    |

| C308.6 |     |     | 3   | 3   |     |     | 2   |     |     |      |      | 1    |

| C303   | 2   | 3   | 3   | 3   | 2   | 3   | 2   | 2   |     |      | 2    | 1    |

| CO'S   | PSO1 | PSO2 | PSO3 |

|--------|------|------|------|

| C308.1 |      |      |      |

| C308.2 | 3    |      |      |

| C308.3 | 3    | 3    | 2    |

| C308.4 | 3    | 3    | 2    |

| C308.5 |      |      |      |

| C308.6 |      |      |      |

| C308 | 3 | 3 | 2 |

|------|---|---|---|

| C300 | 3 | ) | 4 |

#### **SYLLABUS**

| COURSE |                  |          | YEAR OF      |

|--------|------------------|----------|--------------|

| CODE   | COURSE NAME      | L-T-P-C  | INTRODUCTION |

| EC308  | Embedded Systems | 3-0-0 -3 | 2016         |

**Prerequisite:** EC206 Computer Organization, EC305 Microprocessors & Microcontrollers

## Course objectives:

- To have a thorough understanding of the basic structure and design of an Embedded System

- To study the different ways of communicating with I/O devices and standard I/O interfaces.

- To study the basics of RTOS for Embedded systems.

- To study the programming concepts of Embedded Systems

- To study the architecture of System-on-Chip and some design examples.

Syllabus: Introduction to Embedded Systems, Embedded system design process, Serial and parallel communication standards and devices, Memory devices and device drivers, Programming concepts of embedded programming - Embedded C++ and embedded java, Real Time Operating Systems Micro C/OS-II.

## Expected outcome:

The students will be able to:

- i. Understand the basics of an embedded system

- ii. Develop program for an embedded system.

- iii. Design, implement and test an embedded system.

#### Text Books:

- David E. Simon, An Embedded Software Primer, Pearson Education Asia, First Indian Reprint 2000.

- Wayne Wolf, Computers as Components: Principles of Embedded Computing System Design, Morgan Kaufman Publishers - Elsevier 3ed, 2008

### References:

- Frank Vahid and Tony Givargis, Embedded Systems Design A Unified Hardware / Software Introduction, John Wiley, 2002

- 2. Iyer Embedded Real time Systems, 1e, McGraw Hill Education New Delhi, 2003

- 3. K.V. Shibu, Introduction to Embedded Systems, 2e, McGraw Hill Education India, 2016.

- Lyla B. Das, Embedded Systems: An Integrated Approach, 1/e , Lyla B. Das, Embedded Systems, 2012

- 4. Rajkamal, Embedded Systems Architecture, Programming and Design, TMH, 2003

- 5. Steve Heath, Embedded Systems Design, Newnes Elsevier 2ed, 2002

- 6. Tammy Noergaard, Embedded Systems Architecture, A Comprehensive Guide for Engineers and Programmers, Newnes Elsevier 2ed, 2012

|        | Course Plan                                                                                                                                                                                                                                                                                                                                                  |       |                              |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------|

| Module | Course content                                                                                                                                                                                                                                                                                                                                               | Hours | End<br>Sem.<br>Exam<br>Marks |

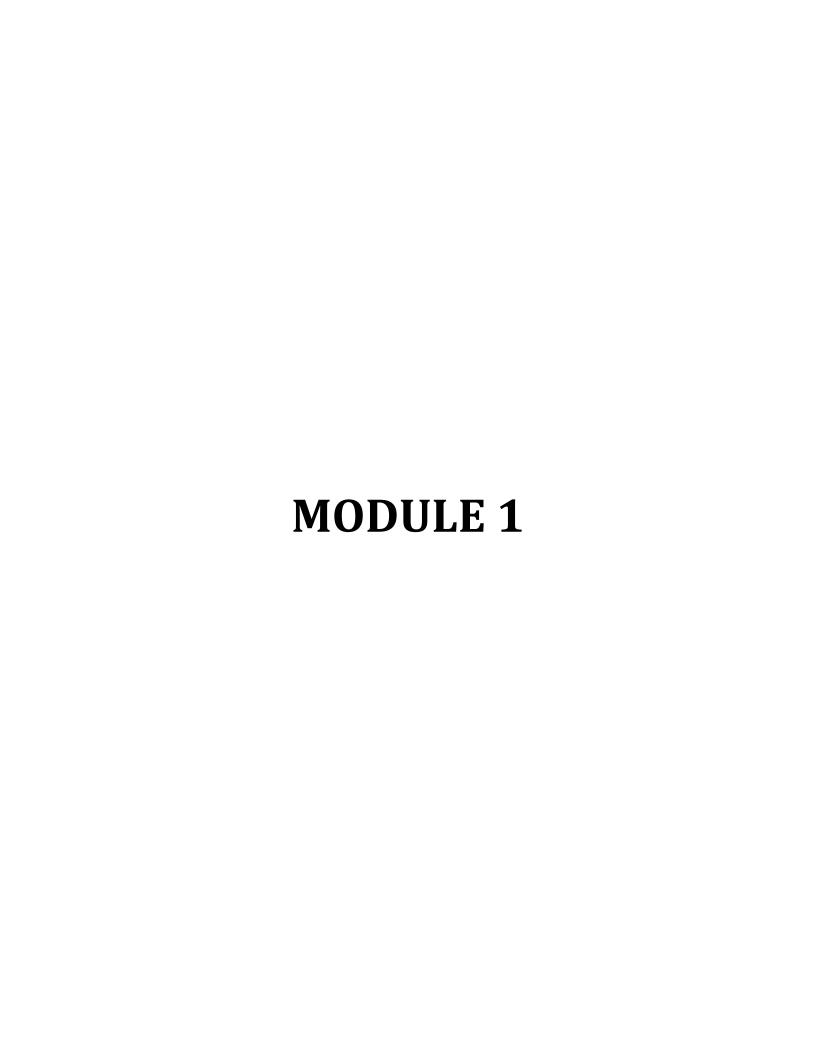

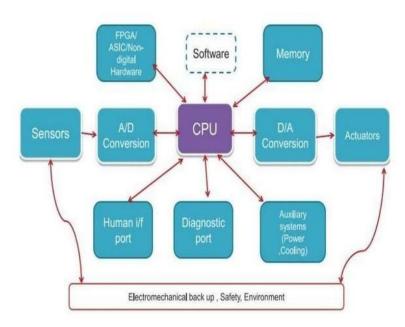

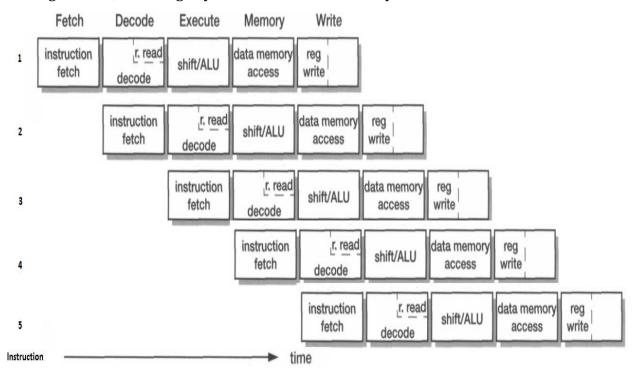

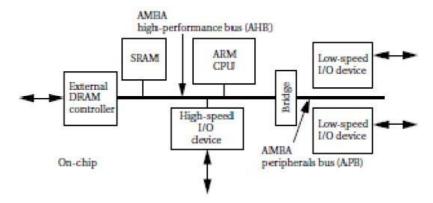

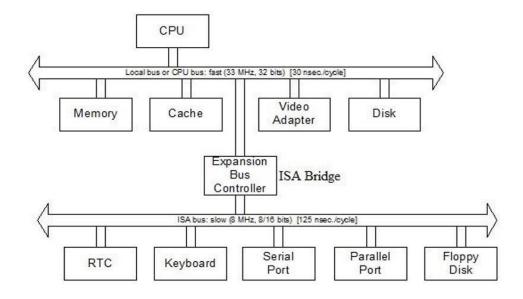

| I      | Introduction to Embedded Systems— Components of embedded system hardware—Software embedded into the system — Embedded Processors - CPU architecture of ARM processor (ARM9) — CPU Bus Organization and Protocol.                                                                                                                                             | 4     | 15                           |

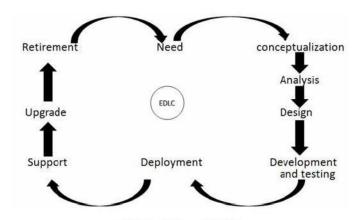

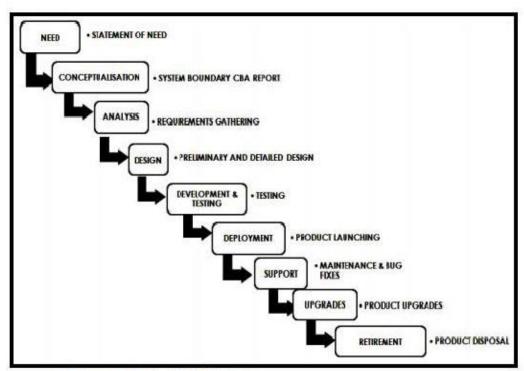

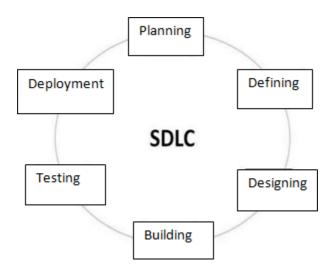

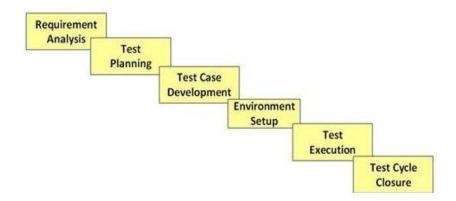

|        | Design and Development life cycle model - Embedded system design process - Challenges in Embedded system design                                                                                                                                                                                                                                              | 3     |                              |

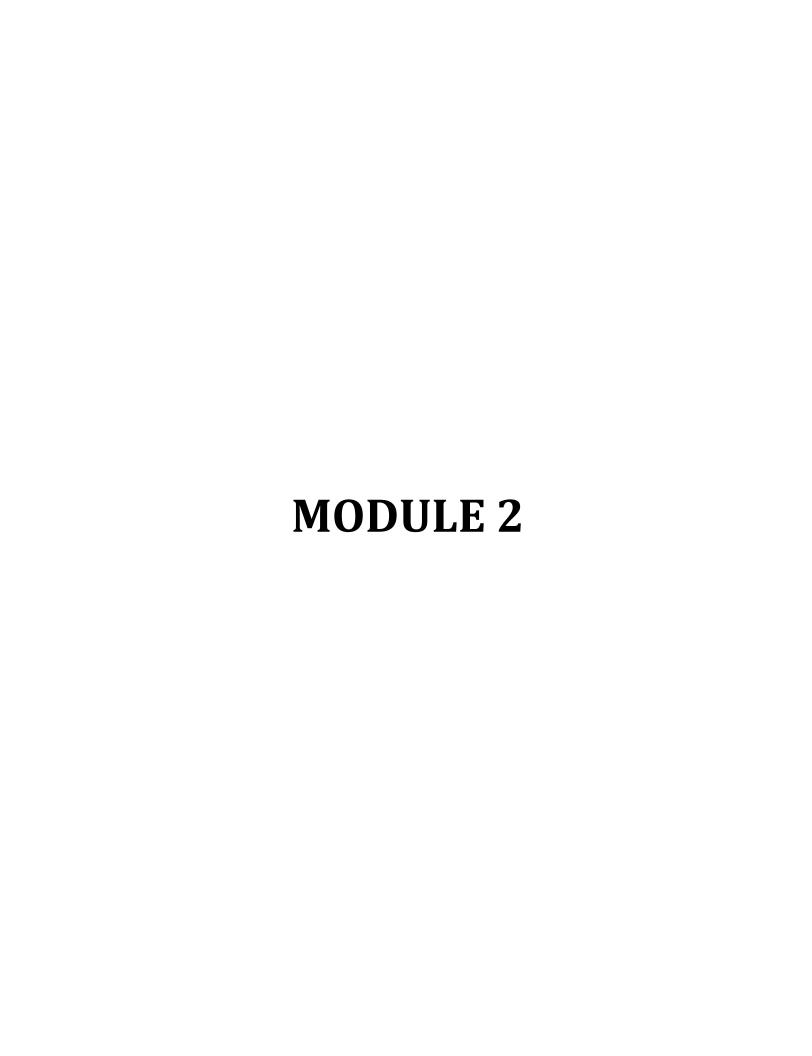

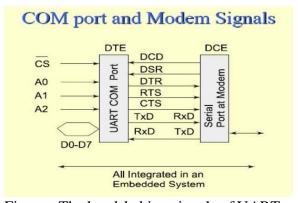

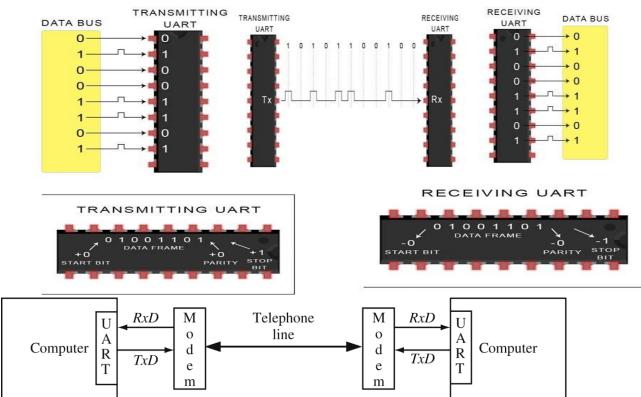

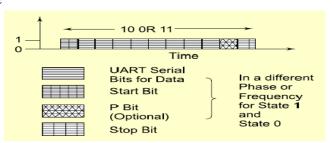

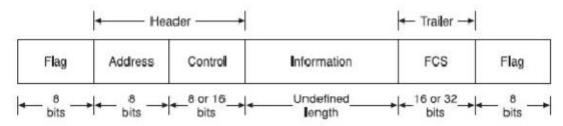

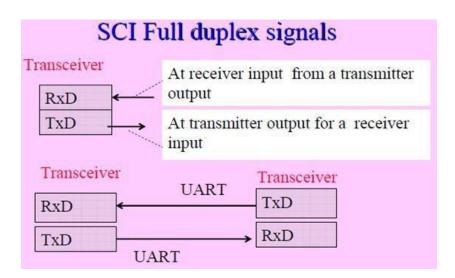

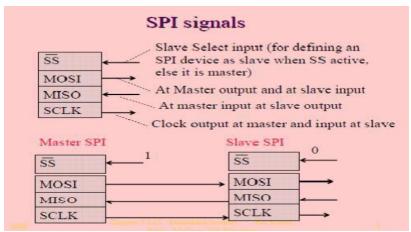

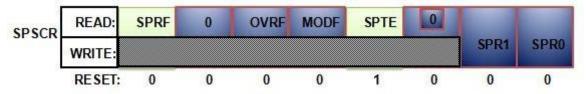

| 17     | Serial Communication Standards and Devices - UART, HDLC, SCI and SPI.                                                                                                                                                                                                                                                                                        | 3     | 15                           |

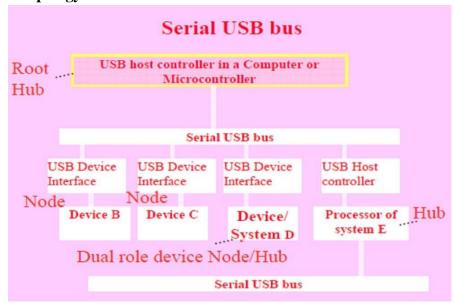

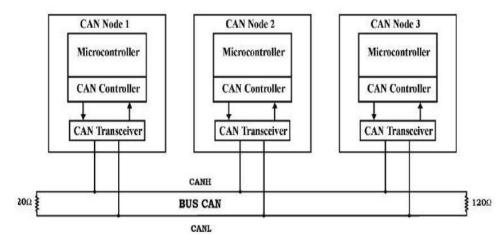

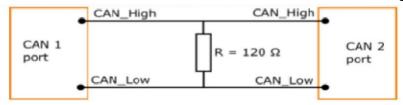

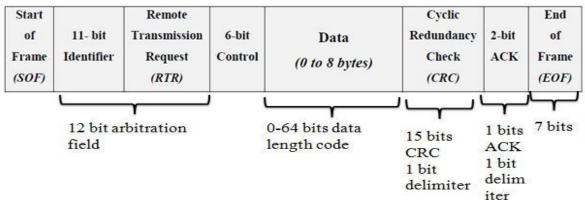

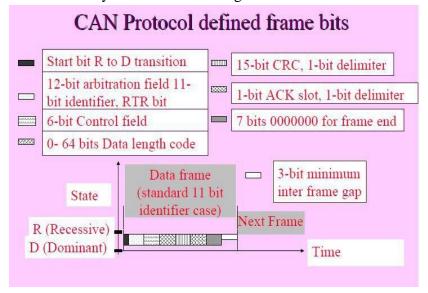

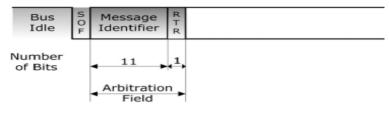

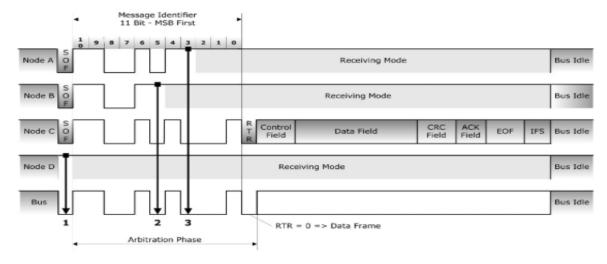

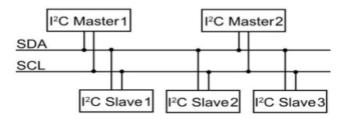

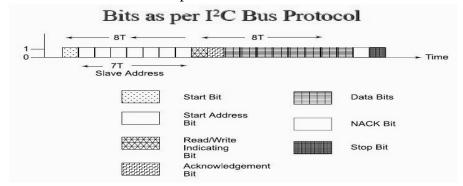

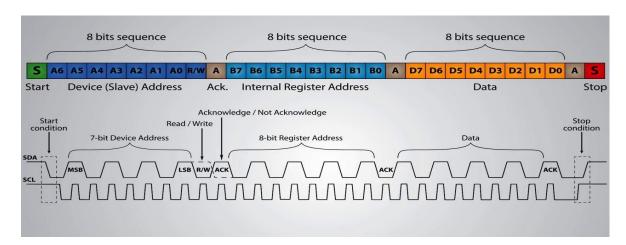

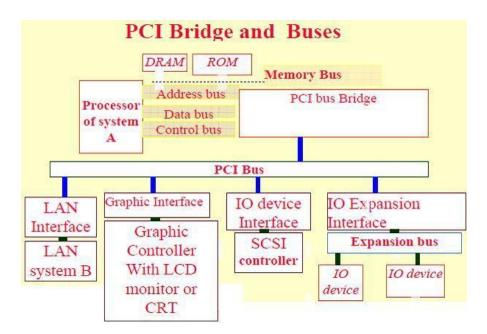

| II     | Serial Bus Protocols - I2C Bus, CAN Bus and USB Bus. Parallel communication standards ISA, PCI and PCI-X Bus.                                                                                                                                                                                                                                                | 3     | 15                           |

|        |                                                                                                                                                                                                                                                                                                                                                              |       |                              |

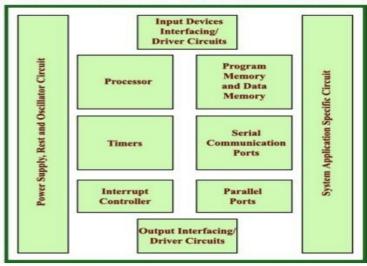

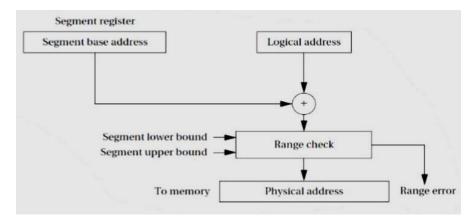

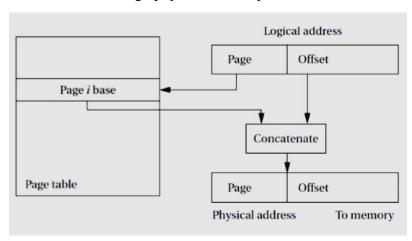

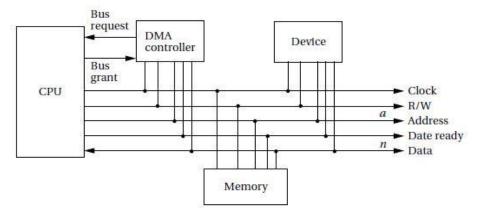

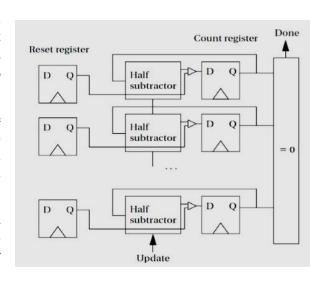

| III    | Memory devices and systems - memory map - DMA - I/O<br>Devices - Interrupts - ISR - Device drivers for handling ISR -<br>Memory Device Drivers - Device Drivers for on-board bus.                                                                                                                                                                            | 6     | 15                           |

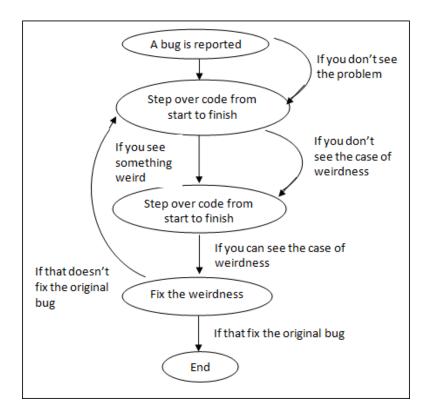

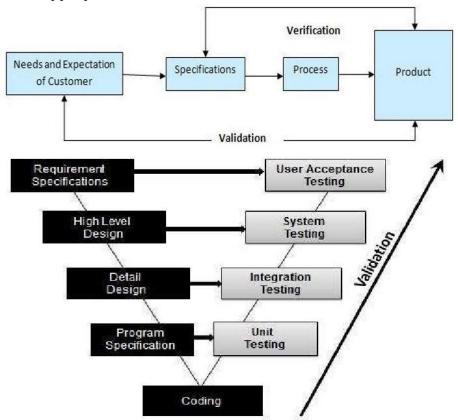

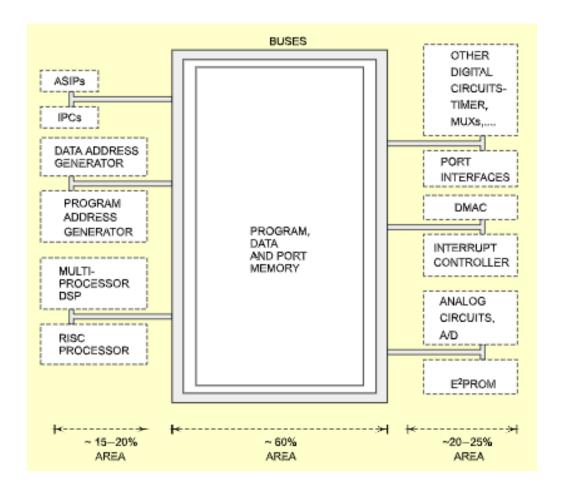

| IV     | Programming concepts of Embedded programming – Features of Embedded C++ and Embedded Java (basics only). Software Implementation, Testing, Validation and debugging, system-on-chip.                                                                                                                                                                         | 6     | 15                           |

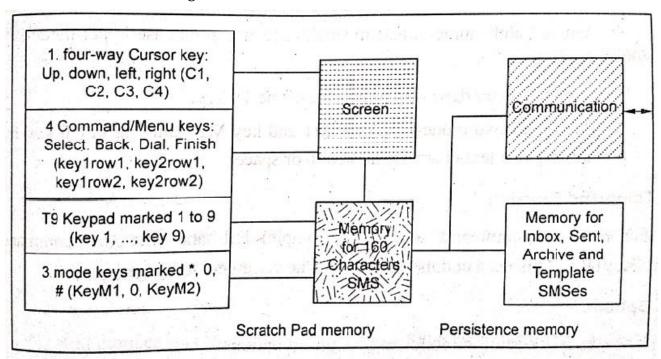

|        | Design Examples: Mobile phones, ATM machine, Set top box                                                                                                                                                                                                                                                                                                     | 1     | 0                            |

|        | SECOND INTERNAL EXAM                                                                                                                                                                                                                                                                                                                                         |       |                              |

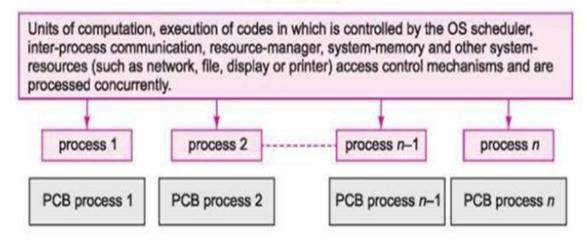

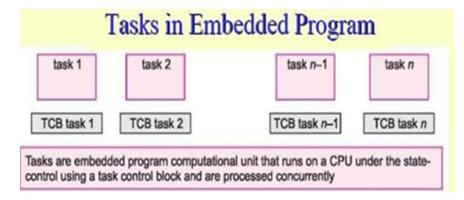

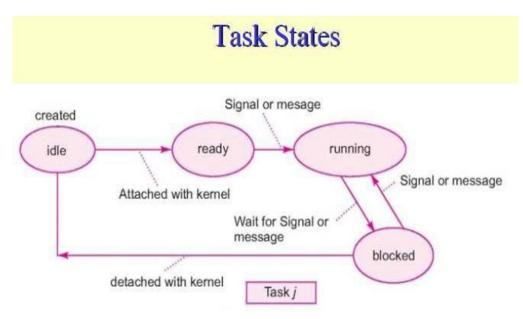

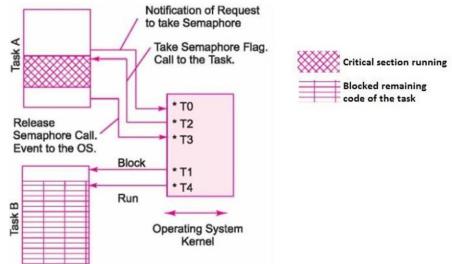

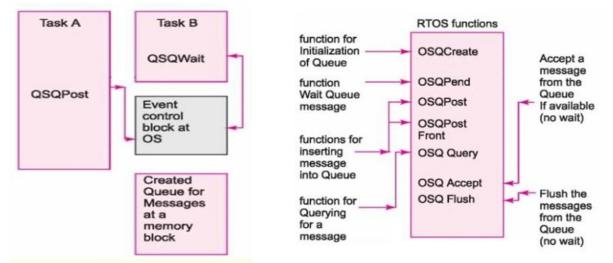

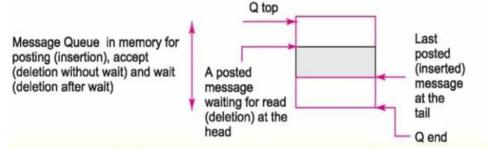

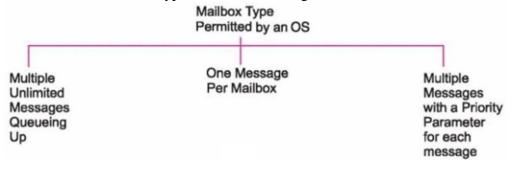

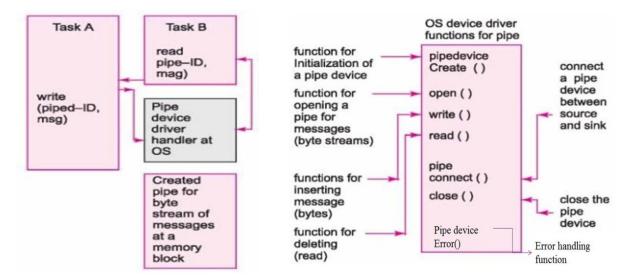

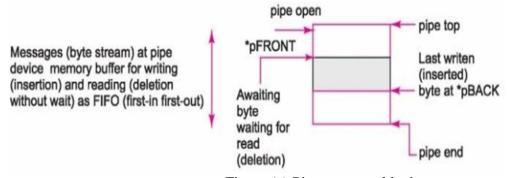

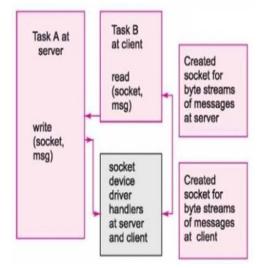

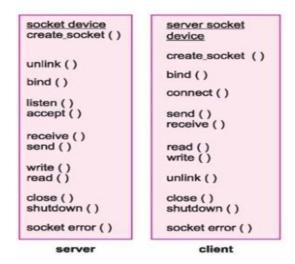

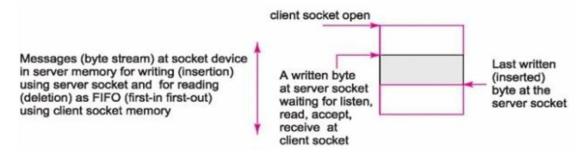

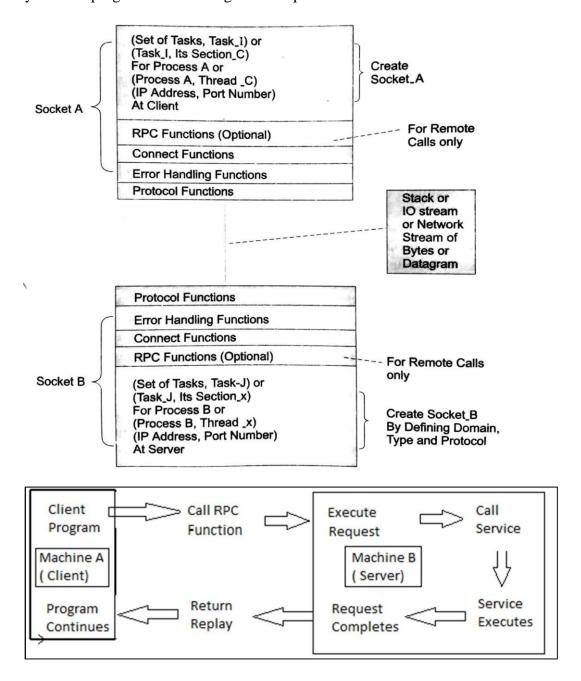

| V      | Inter Process Communication and Synchronization -Process, tasks and threads -Shared data- Inter process communication - Signals - Semaphore - Message Queues - Mailboxes - Pipes - Sockets - Remote Procedure Calls (RPCs).                                                                                                                                  | 8     | 20                           |

| VI     | Real time operating systems - Services- Goals - Structures - Kernel - Process Management - Memory Management - Device Management - File System Organization.  Micro C/OS-II RTOS - System Level Functions - Task Service Functions - Memory Allocation Related Functions - Semaphore Related Functions.  Study of other popular Real Time Operating Systems. | 8     | 20                           |

|        | END SEMESTER EXAM                                                                                                                                                                                                                                                                                                                                            | •     |                              |

## Question Paper Pattern (End semester exam)

Maximum Marks: 100 Time: 3 hours

The question paper shall consist of three parts. Part A covers modules I and II, Part B covers modules III and IV, and Part C covers modules V and VI. Each part has three questions uniformly covering the two modules and each question can have maximum four subdivisions. In each part, any two questions are to be answered. Mark patterns are as per the syllabus with 100 % for theory.

# **QUESTION BANK**

## **MODULE I**

| Q:NO: | QUESTIONS                                                                                | co  | KL | PAGE NO: |

|-------|------------------------------------------------------------------------------------------|-----|----|----------|

| 1     | Define system and embedded system with example                                           | CO1 | K2 | 2        |

| 2     | Discuss briefly challenges in embedded system design                                     | CO1 | КЗ | 22       |

| 3     | Compare RISC & CISC architecture                                                         | CO1 | К3 | 14       |

| 4     | List out classification of embedded system with example and also define embedded system. | CO1 | КЗ | 3        |

| 5     | Discuss the challenges in embedded system design.                                        | CO1 | K2 | 22       |

| 6     | Explain various types of embedded system software                                        | C01 | K2 | 11       |

| 7     | Discuss about CPU architecture of ARM processor                                          | CO1 | K2 | 16       |

| 8     | Explain about embedded processors                                                        | C01 | K2 | 7        |

| 9     | Explain the different embedded system development life cycle models                      | CO1 | K2 | 21       |

| 10    | Draw the neat diagram of ARM9 architecture and explain it.                               | C01 | K2 | 17       |

| 11    | Explain the components of embedded system.                                               | CO1 | K2 | 3        |

|    | MODULE II                                                             |     |    |    |  |  |  |  |

|----|-----------------------------------------------------------------------|-----|----|----|--|--|--|--|

| 1  | Write a note about UART                                               | CO2 | K1 | 25 |  |  |  |  |

| 2  | Draw the diagram of I <sup>2</sup> C frame format. Explain each field | CO2 | K2 | 41 |  |  |  |  |

| 3  | Explain different data transfer modes used in USB bus standard        | CO2 | K2 | 35 |  |  |  |  |

| 4  | Describe the various modes of serial communication                    | CO2 | K2 | 27 |  |  |  |  |

| 5  | Draw the HDLC frame and explain it                                    | CO2 | K2 | 28 |  |  |  |  |

| 6  | Write a short notes on UART & HDLC                                    | CO2 | K2 | 28 |  |  |  |  |

| 7  | Describe bus arbitration. Explain the bus                             | CO2 | K2 | 13 |  |  |  |  |

|    | arbitration scheme used in CAN bus with example.                      |     |    |    |  |  |  |  |

| 8  | Discuss about CAN bus and USB bus                                     | CO2 | K2 | 34 |  |  |  |  |

| 9  | Explain parallel communication standards ISA & PCI                    | CO2 | K2 | 31 |  |  |  |  |

| 10 | Briefly describe parallel communication standards.                    | CO2 | K2 | 30 |  |  |  |  |

| 11 | Discuss about serial bus protocols I2C bus and CAN bus                | CO2 | K2 | 41 |  |  |  |  |

|    | MODULE III                                                            |     |    |    |  |  |  |  |

| 1  | Draw the hierarchy of memory and explain                              | C03 | K1 | 50 |  |  |  |  |

| 2  | 2.Compare static RAM & dynamic RAM                                    | CO3 | К3 | 51 |  |  |  |  |

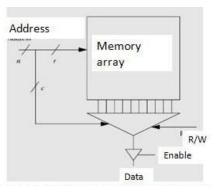

| 3  | Explain about memory system organization                              | CO3 | K2 | 53 |  |  |  |  |

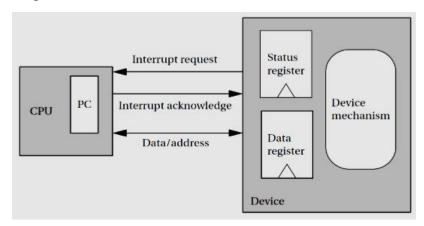

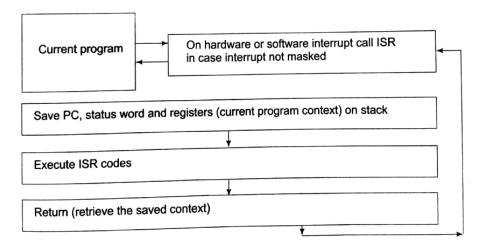

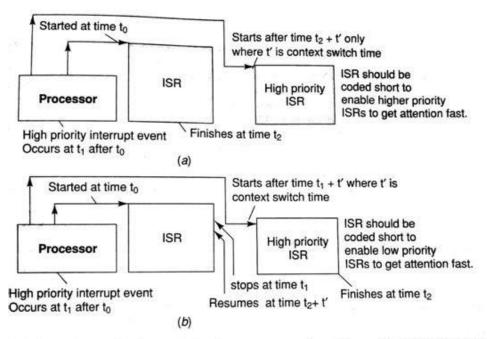

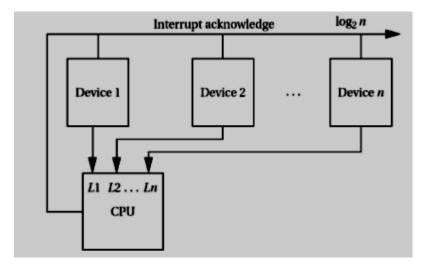

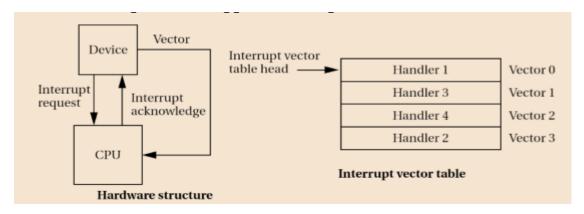

| 4  | Explain the concept of interrupt service routine                      | CO3 | К3 | 61 |  |  |  |  |

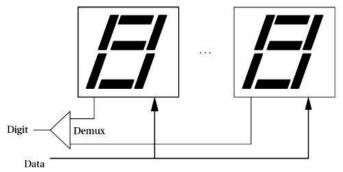

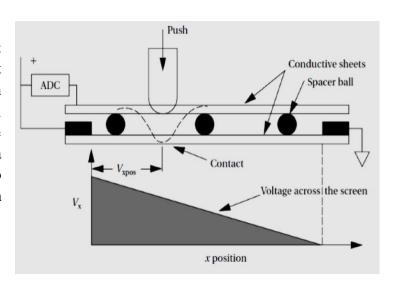

| 5  | Explain any four type I/O types used in embedded systems              | CO3 | К2 | 63 |  |  |  |  |

| 6  | Explain the different modes in which a DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CO3 | K2  | 54 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----|

|    | controller transfers data between                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |     |    |

|    | memory and peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |    |

| 7  | Describe about interrupt driven input and output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CO3 | K2  | 55 |

|    | Point out the different steps for reading port bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |     |    |

|    | received from external system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |     |    |

| 8  | Explain about memory device drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CO3 | К3  | 66 |

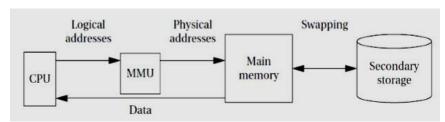

| 9  | Summarize memory management device driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CO3 | K2  | 67 |

|    | pseudo code with examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |    |

| 10 | Interpret about I/O Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CO3 | КЗ  | 68 |

|    | MODULE IV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |    |

|    | MODULE IV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |    |

| 1  | Evalois about various Como quammina alementa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CO4 | 1/2 | 75 |

| 1  | Explain about various C programming elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CO4 | КЗ  | /5 |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |    |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |    |

| 2  | Discuss about embedded programming in Java                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CO4 | K2  | 78 |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |    |

| 3  | Distinguish macros and functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CO4 | K2  | 76 |

| 4  | Describe about use of pipe and table with a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CO4 | K2  |    |

|    | diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |     |    |

| 5  | Compare C programming and embedded C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CO4 | K2  | 76 |

|    | programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |     |    |

| 6  | Discuss about array and multi-dimensional array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CO4 | K2  | 77 |

|    | with example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |     |    |

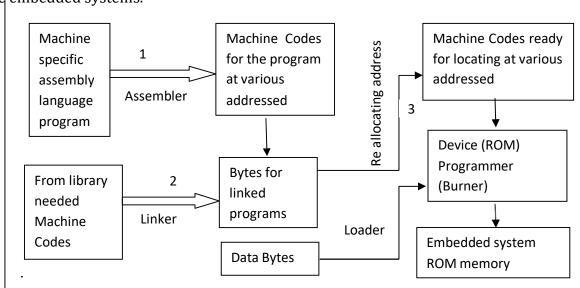

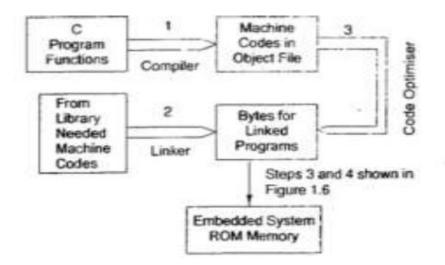

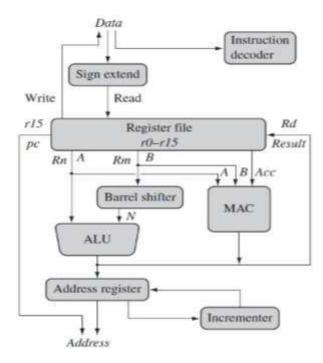

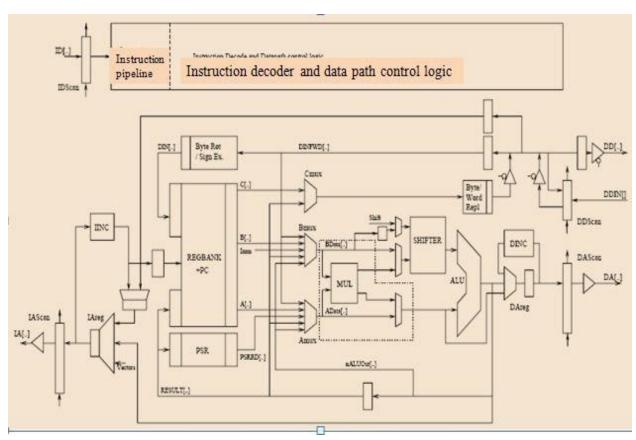

| 7  | Discuss the hardware and software components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CO4 | КЗ  | 81 |